北京立萨科技有限公司

咨询热线:010-82488292

公司电话:010-82488292

公司传真:010-82611646

企业邮箱:sales@lisatech.cn

地址:北京市海淀区中关村大街19号 新中关大厦B座南翼15层1507室

AM335X MCASP与 AIC3100调试心得

摘要 : 首先先确定,AIC3100部分的接口电路是否正常,可以将AIC3100配置为loopback模式,对麦克风进行讲话,耳机可以听到声音,可以设置page1 reg35寄存器,

首先先确定,AIC3100部分的接口电路是否正常,可以将AIC3100配置为loopback模式,对麦克风进行讲话,耳机可以听到声音,可以设置page1 reg35寄存器,

修改AM335X_StarterWare_02_00_00_06下的mcasp代码,因为他们使用的是AIC3106,MCASP1,而我们使用AIC3100,MCASP0,所以修改对应的代码,

修改完成后,刚开始无法检测初始化序列,后来检查原因才知道,MCASP1是让AIC3106提供BCLK和WCLK信号,那么我们也配置对应的AIC3100,让时钟输出,调试基本完成,以下是调试的笔记记录

IIS接口有4根线:

IISDI:串行数据输入

IISDO:串行数据输出

IISLRCK:左右声道选择,由主设备产生信号,=0就是左声道

IISCLK:串行数据时钟,由主设备产生信号

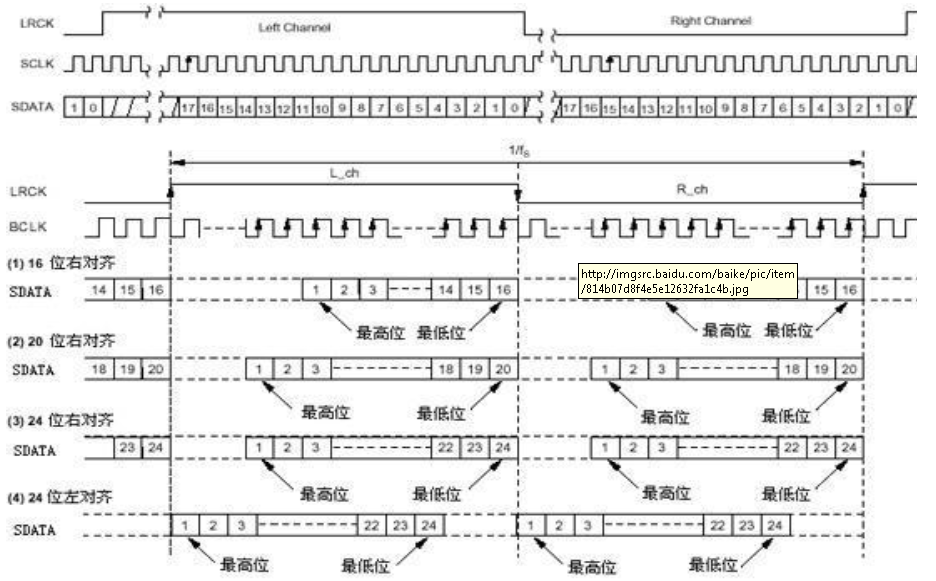

IIS数据格式分为:左对齐、右对齐、IIS格式

功能模块:

time-division multiplexed (TDM),IIS格式也是TDM里面的其中一种,

TDM通常是在集成电路之间的通讯,例:多个AD、DA、S/PDIF模块之间的通讯

TDM格式一半由3部分组成:始终,数据线,同步帧信号

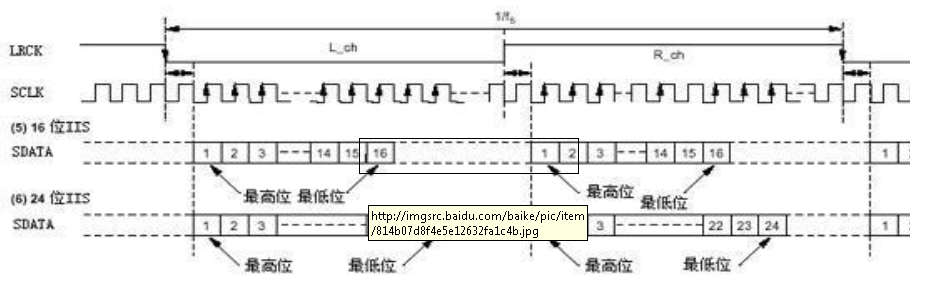

一半分为bit、word、slot,bit=每1个bit,word=16个bit,slot=例如在左声道,一共要发20bit,已经发了16bit,那么还有4bit,也要打出时钟,那么16+4bit就是一个slot

Slots也被称为time slots 或 channels

S/PDIF,DIT是其中的一种格式

digital audio interface transmission (DIT).

Serializers:实际就是对应axr引脚,用于收发数据

在CPU中的IO引脚信息

用AXR引脚来读写数据,相当于上面的DI、DO

发送时钟:

AHCLKX:发送高频主时钟(输出)

ACLKX:发送位时钟(输出)

接收时钟:

AHCLKR:接收高频主时钟

ACLKR:接收位时钟

AFSX:发送帧同步信号(IIS中,左右声道切换)

AFSR:接收帧同步信号

AMUTEIN:静音输入,AM335X没有

AMUTE:静音输出,AM335X没有

McASP的时钟发生器的时钟源可以源自:

内部 将内部时钟源通过两个分频器产生时钟;

外部 直接由ACLKX/R引脚输入;

混合 一个外部高频时钟输入到McASP的AHCLKX/R一脚,然后被分频器进行分频。

三种传输模式:突发传输模式,TDM和DIT

突发模式:不是用于音频数据的传输,例如在两个DSP之间通讯

TDM:可以用于和多个ADC或DAC芯片之间数据传输,IIS是工作在此模式下

DIT:支持以s/pdif、AES-3、IEC-60958格式传输音频数据

McASP使用IIS协议,也支持DIT协议

McASP包括发射与接收两部分,它们可以使用不同时钟,不同传输模式,工作完全独立。发射和接受能够工作在同步状态,

McASP的没有使用到的管脚能被配置成通用I/O管脚

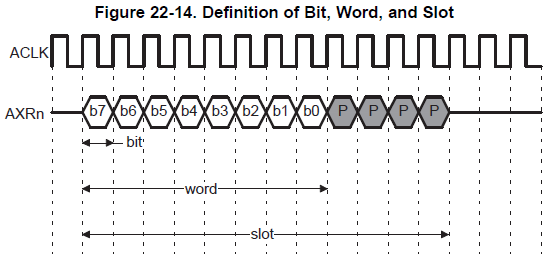

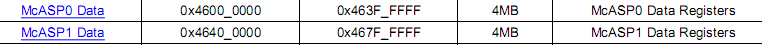

寄存器 ,起始地址如上图

REV:版本号寄存器

描述了这几个IO的作用,控制Io的输入或输出

PFUNC:引脚功能寄存器,描述了AXRn, ACLKX, AHCLKX, AFSX, ACLKR, AHCLKR, and AFSR引脚的用于音频还是GPIO

AFSR、AHCLKR、ACLKR、AFSX、AHCLKX、ACLKX、AMUTE、AXR[5-0]:

以上引脚=1用于GPIO,=0用于音频

PDIR:引脚方向寄存器,不管PFUNC配置成什么,都要设置好输入输出方向,对于时钟要设置为输出

和上面一样,=0设置成输入,=1设置成输出

PDOUT:引脚输出1或速出0,只支持GPIO输出模式

PDIN:引脚读取

PDSET:引脚设置1

PDCLR:引脚设置0

GBLCTL:复位寄存器,写0复位,写入后一定要读回判断状态

XFRST:发送帧同步发生器复位,=0复位

XSMRST:发送状态机复位

XSRCLR:发送序列激活

XHCLKRST:发送高频率的时钟分频器复位,=0复位,=1开始运行

XCLKRST:发送时钟分频器复位,=0复位,=1开始运行

RFRST:接收帧同步发生器复位,=0复位

RSMRST:接收状态机复位,=0复位,=1启动

RSRCLR:接收序列激活

RHCLKRST:接收高频时钟复位,=1开始运行

RCLKRST:接收内部时钟分频器复位,写0复位,=1开始运行

AM335X没有此引脚

AMUTE:静音寄存器,如果检测到错误,是否驱动AMUTE引脚

XDMAERR:发送DMA错误,是否驱动AMUTE引脚

RDMAERR;接收DMA错误,是否驱动AMUTE引脚

XCKFAIL:发送时钟故障,是否驱动AMUTE引脚

RCKFAIL:接收时钟故障,是否驱动AMUTE引脚

XSYNCERR:发送帧同步错误,是否驱动AMUTE引脚

RSYNCERR:收到帧同步错误,是否驱动AMUTE引脚

XUNDRN:传输欠载错误,是否驱动AMUTE引脚

ROVRN:接收溢出错误后,是否驱动AMUTE引脚

INSTAT:是否启动AMUTEIN引脚的错误检测

INEN:在发生AMUTEIN错误时,驱动AMUTE引脚

INPOL:音频静音(AMUTEIN)极性选择

MUTEN:AMUTE引脚状态,=0停止检测,=1如果检测到错误引脚拉高,=2拉低

DLBCTL:回环测试模式

MODE:

ORD:

DLBEN:=1启动回环模式

DITCTL:主要配置DITEN位,用于什么模式

VB:有效位在奇数Clock位

VA:有效位在偶数Clock位

DITEN:=0 DIT模式禁用,传输在TDM或突发模式,=1启用DIT解码模式

接收相关的

RGBLCTL:和GBLCTL一样,只是单独控制接收部分

XFRST、XSMRST、XSRCLR、XHCLKRST、XCLKRST:都是只读的,是发送的内容

RFRST、RSMRST、RSRCLR、RHCLKRST、RCLKRST:可能可以单独的操作

格式化单元用到的寄存器

RMASK:接收屏蔽寄存器,没有用到的数据将会被屏蔽

例如要接收16bit的数据,那么设置为(1<<16)-1即可,写1为要保留的数据

如果收发的是IIS格式,那么选择MSB在前,左对齐,RDATDLY = 01 (1 bit delay)

RFMT:接收位格式寄存器

RDATDLY:接收位延时,延时多少个CLk开始接收,如果是IIS协议这里要是1

RRVRS:接收数据是高位在前还是低位在前,=1是高位在前

RPAD:未使用的bit在slot里,此寄存器来写入有多少个未使用的bit

如果是3和RPBIT有关联、 在slot里有多少没用的bit,因为bit构成word,word+额外bit构成slot

RPBIT:当RPAD=2时,由这个寄存器指定在slot里,有多少个没用的bit

RSSZ:接收slot的大小

RBUSEL:接收的数据来源,从dat还是配置寄存器,使用DMA时,要设置为0

RROT:数据右旋转移动多少bit

AFSRCTL:接收帧同步控制寄存器

RMOD:接收帧同步模式选择,配置IIS模式等(IIS模式写2)

FRWID:接收帧同步信号的宽度

FSRM:接收帧同步的时钟源,内部或外部时钟,然后在FSRP中配置信号极性

FSRP:接收帧同步的时钟极性选择,上或下边沿进行同步

时钟控制

ACLKRCTL:ACLKR接收时钟控制

CLKRP:输入时钟上升沿还是下降沿有效

CLKRM:输入源选择,从内部或从外部产生ACLKR信号,如果是内部选择还要注意是从XCLK还是RCLK产生时钟信号

CLKRDIV:接收时钟分频比

AHCLKRCTL:AHCLKR接收高频时钟控制寄存器

HCLKRM:选择接收高频时钟的时钟源(内部输入,或外部AHCLKR输入)

HCLKRP:接收高频时钟是否反向,接收到的高频时钟是否反向给ACLKR

HCLKRDIV:内部AUXCLK时钟输入,时钟分频

RTDM:接收TDM时间槽

RTDMS:接收时间槽有效,IIS配置(1<<2)-1

RINTCTL:接收中断控制寄存器,可以产生中断

RSTAFRM:开始接收帧

RDATA:接收数据就绪中断

RLAST:接收最后一个槽?

RDMAERR:接收DMA错误

RCKFAIL:接收时钟故障

RSYNCERR:意外接收帧同步中断

ROVRN:=1接收溢出中断开启

RSTAT:接收状态

RTDMSLOT:当前TDM时间是 odd还是even

RSLOT:只读

RCLKCHK:接收时钟检查

RCNT:只读

RMAX:接收时钟最大的边界

RMIN:接收时钟最小的边界

RPS:接收时钟的分频比

REVTCTL:接收DMA事件

RDATDMA:=1接收数据DMA请求使能

发送相关的,和接收的类似含义,具体可以看接收部分

XGBLCTL:和GBLCTL一样,只是单独控制接收部分

发送格式相关的

XMASK:发送屏蔽寄存器,没有用到的数据将会被屏蔽

例如要发送16bit的数据,那么设置为(1<<16)-1即可,写1为要保留的数据

XFMT

XBUSEL:和DMA相关,=1使用DMA操作配置寄存器,=0操作数据寄存器

AFSXCTL:发送帧同步配置

XMOD:选择传输的模式,=2h-20h 2-slot TDM (I2S mode) to 32-slot TDM.(IIS要设置为2)

FXWID:帧同步信号的宽度选择是1bit还是1word

FSXM:内部或外部的产生帧同步信号,在FSXP中配置极性

FSXP:帧同步信号的极性,高电平或低电平有效

输出时钟配置

ACLKXCTL:ACLKX输出时钟源配置

CLKXP:内部XCLK时钟输入的极性选择位,=0上升沿,注意这里和接收是相反的

ASYNC:和接收时钟有关,可以选择接收时钟是XCLK还是RCLK

如果=1,那么接收发发送是独立不同步的,独立的时钟和独立的帧同步信号

如果=0,那么发送和接收同步运行,相同的时钟和帧同步信号,接收可以有不同的格式,但是单元大小是兼容的,如果是IIS必须同步,因为只用1个时钟

难道是IIS协议必须这样配置?

CLKXM:传输bit时钟源选择,从ACLKX输出,=0外部时钟,=1内部时钟(XCLK)

CLKXDIV:如果CLKXM配置为外部时钟那么此寄存器为分频时钟比

AHCLKXCTL:AHCLKX高速输入时钟的配置

HCLKXM:高频时钟从外部输入或CPU内部产生,外部从AHCLKX引脚输入

HCLKXP:高频时钟输入,是否反相后给ACLKX做时钟源

HCLKXDIV:内部AUXCLK时钟输入,分频比

XTDM

XINTCTL:发送中断寄存器,写1开启中断

XSTAT:接收状态寄存器,写1清除

XERR

XDMAERR

XSTAFRM

XDATA:=1代表寄存器是空,可以继续写入数据,并产生AXEVT事件,

XLAST

XTDMSLOT

XCKFAIL

XSYNCERR

XUNDRN

XSLOT

XCLKCHK

XEVTCTL

仅在DIT模式支持

DITCSRA0~ DITCSRA5:一共有6个

左声道状态寄存器

DITCSRB0~ DITCSRB5:一共有6个

右声道状态寄存器

DITUDRA0~ DITUDRA5:一共有6个

DIT左声道用户数据寄存器

DITUDRB0~ DITUDRB5:一共有6个

DIT右声道用户数据寄存器

有4路收发IO,分别对应

SRCTL 0~3:一共有4个寄存器,一个IO对应1个寄存器配置

RRDY:接收buf收到数据,收到数据时=1,只读

XRDY:发送buf已经为空,准备好,只读

DISMOD:PFUNC = 0,那么引脚的输出状态,三态,输出高、低

SRMOD:设置为发送还是接收,或无效状态

XBUF0~ XBUF3:共4个,发送buf寄存器

RBUF0~ RBUF3:共4个,接收buf寄存器

音频的FIFO控制 音频控制器起始地址 + 0x1000 偏移

WFIFOCTL:发送FIFO控制寄存器

WENA:写FIFO使能位,=1开启,

WNUMEVT:FIFO的大小?

WNUMDMA

WFIFOSTS:发送FIFO状态寄存器,只读

WLVL:当前有多少个字在FIFO中

RFIFOCTL:读取FIFO控制

RENA:读FIFO使能位

RNUMEVT:在FIFO中有多少个数据,产生一次DMA事件(收到多少字节产生DMA请求)

RNUMDMA:最少多少个数据发生DMA事件

RFIFOSTS:读取FIFO状态寄存器

接收和发送缓冲区

RBUF:读FIFO buf地址

XBUF:写FIFO buf地址

这个用于DMA,发送和接收分别有3路FIFO,每触发一次,都将这个加入到dma,然后一直循环,加快读写的连续性?

以上这2个地址,直接对应到RBUF、XBUF,两个buf中

笔记:

序列化Serializers

每个序列化包括,

移位寄存器XRSR、数据寄存器XRBUF、控制寄存器SRCTL(每个数据IO对应1个)

XRBUF保留原始数据,当CPU读取时,会格式化数据,然后给CPU内存

格式单元,Format Unit

有2个,发送和接收,可以屏蔽掉某些位和增加符号扩展

初始化步骤

复位MCASP模块,GBLCTL=0

配置发送和接收时钟

配置IO口,如果是时钟输出等,要配置PDIR为输出模式,PDIR最后配置,先设置好时钟后,配置

如果开启DMA,那么接收到AXEVT事件后,DMA会被自动服务

CPU中断是依靠AXINT事件

有2个复位源,软件和硬件复位

软件复位通过GBLCTL寄存器,复位发送和接收等IO

硬件复位,

TDM模式中所有的数据为AXR[n]都是与时钟同步,同时数据传输是连续的,数据单元之间没有延迟,单元N的最后一位后面紧跟着下一单元的第一位。同时帧同步信号可能会相对于第一个单元的第一位有0,1或者2个周期的延迟。

一般通过DMA端口来访问McASP的XRBUF寄存器,通过DMA端口,DMA/CPU可以仅仅通过一个地址来对所有的串行器服务,也就是CPU /DMA可以通过DMA端口按照升序的顺序循环地对每个被使能的接收/发送通道进行写/读取操作。如有4个通道(1,3,5,6)被使能为接收通道,则读 取的时候需要进行4次读取操作,得到的数据分别为通道1,3,5,6的数据。与DMA端口访问不同,通过外围配置总线访问访问XRBUF 时,CPU/DMA必须提供每次访问的准确XBUFn或者RBUFn地址。推荐使用DMA端口对McASP进行访问

对于McASP来说,DMA事件的产生和CPU中断产生之间是有区别的,DMA事件是在数据准备就绪后自动产生的,不需要对寄存器进行设置,而CPU中断的产生需要将XINTCTL/RINTCTL寄存器中的中断使能。

当对McASP初始化的过程中,将McASP中相应的串行器带出复位状态后(GBLCTL寄存器中的XSRCLR位从0变到1),会使得传输状态寄存器 XSTAT中的XDATA位从0变为1,即表示发送串行器的XBUF中内容为空,需要写入数据,该变化会触发一个EDMA事件(也可以触发中断事件,如果 中断使能的话),使得EDMA对XBUF进行写操作,并且每次XBUF的数据被移入XRSR后XDATA都会置位,触发EDMA数据传输,直到EDMA中 的计数器达到0。

ACLKX和AHCLKX可以做时钟输入,也可以做时钟输出?

时钟的配置例子:

假设,模块时钟为26M,IIS格式,192K的频率,slot是32bit

系统时钟周期 = 1/26 = 38.5ns

ACLKX时钟计算:

IIS格式有左右两个声道,一个声道(slot)有32Bit,那么就是32*2=64Bit,2个Slot相加

采样频率为192K,周期=1/192K/64=81.4ns

DMA(AXEVT)事件,

1/192k/2=2604ns 因为一组产生2个AXEVT事件

AXEVT的延时

5组MCASP时钟??(这个是什么,为什么是5组)

38.5ns * 5 = 192.5ns

设置时间:

3组MCASP时钟 + 4个ACLKX周期

=(38.5ns * 3) + (4 * 81.4ns)

=441.1ns

处理器服务时间

=Time Slot – AXEVT延时 – 设置时间

= 2604 ns - 441.1 ns - 192.5 ns

= 1970.4 ns

上一篇:Videostrong商显主板RK3288 I2C 通讯介绍资料1970-01-01

下一篇:BB-Black之PRU-ICSS简析1970-01-01

文章推荐

- RK3288底板+核心板设计过程

- RK3288广告机硬件和软件调试心得

- 一款基于TI Sitara Cortex-A8 AM3358的嵌入式单板机

- BeagleBone产品采用了德州仪器推出的Sitara AM335x Cortex A8 ARM处理器

- 一个带有HDMI视频输入的VS-RK3288方案

- 瑞芯微vs-rk3288方案定制Android 开发板

- RK3288在人脸识别上的应用及外接双路摄像头

- 德州仪器(TI)工业以太网解决方案

- AM335x ARM Cortex-A8处理器-TI DLP 3D打印机总体解决方案

- 瑞星微RK3288方案设计

- i.MX6Q Cortex-A9新一代智能平台

- i.MX6Q车载全触控智能管理终端解决方案

- AM3354嵌入式充电桩计费控制单元主板方案

- 大联大控股世平推出 TI 、NXP 多领域应用人机交互平台

- 强化物联网“心脏”,智能网关设计详解

- TI AM437x系列处理器为核心的嵌入式开发板Rico Board

- 如何用BB Black制作DAC系统

- 采用AM3352工控核心板进行免疫荧光检测仪解决方案

- 人机交互与TI Sitara处理器的产品性能介绍

- Rockchip RK3399 eMMc 的 DTS 配置说明

| 我要评论: | |

| *内 容: |

|

| 验证码: |

|

共有0条评论